그래프코어 연구는 그래프코어의 최신 하이퍼스케일 IPU-POD128 및 IPU-POD256 시스템에서 혁신적인 컴퓨터 비전 모델 EfficientNet-B4의 훈련을 가속화하여 2시간 이내에 컨버전스에 도달한 방법을 보여 줍니다.

EfficientNet을 사용해야 하는 이유는?

EfficientNet 모델 제품군은 컴퓨터 비전의 최신 기술을 기반으로 비교적 적은 수의 매개변수와 FLOP으로 뛰어난 작업 성능을 제공합니다. 하지만 레거시 프로세서 아키텍처는 EfficientNet을 매우 효율적으로 만드는 많은 속성을 활용할 수 없기 때문에 실질적인 도입에 장애가 됩니다.

예를 들어 EfficientNet에서 제공하는 깊이별 또는 그룹 컨볼루션은 표준 컨볼루션 운영 대비 표현도가 뛰어나고 연산 효율도 높지만, 산술 강도(데이터 이동 대비 연산 비율)가 낮습니다. 이러한 유형의 운영은 메모리와 프로세서 코어 간의 대규모 데이터 전송으로 인해 GPU에서 제대로 수행되지 않습니다. IPU의 메모리 중심 아키텍처를 이용하면 전체 모델과 활성화가 칩에 남아 있어 성능 부하가 높은 데이터 이동을 완화할 수 있습니다.

또한 IPU의 MIMD(Multiple Instruction, Multiple Data) 패러다임은 모델 및 훈련 절차의 여러 차원에 걸쳐 세분화된 병렬 처리를 제공합니다. 따라서 작은 컨볼루션을 사용하고 매우 적은 데이터 샘플을 병렬로 처리하면서 높은 처리량을 달성할 수 있습니다. 이와 반대로, SIMD(Single Instruction, Multiple Data) 아키텍처를 지원하는 GPU는 병렬 처리를 활용하는 방식이 제한되어 있기 때문에, 사용자는 머신러닝 알고리즘의 디자인과 하드웨어에서 달성 가능한 알고리즘 처리량 간에 타협을 진행해야 합니다.

IPU 하드웨어의 이번 가속화는 더 많은 혁신가와 AI 실무자들이 대규모 실제 구현에 EfficientNet 모델의 고효율성을 이용할 수 있는 기회를 제공합니다.

GitHub의 그래프코어 예제는 누구나 IPU에서 EfficientNet 모델 제품군을 포함한 다양한 인기 모델을 곧바로 활용할 수 있음을 보여 줍니다. 이 연습에서는 EfficientNet 성능을 벤치마킹하기 위해 AI 분야에서 자주 사용되는 EfficientNet-B4를 고려합니다.

처리량 최적화

모델 분산

데이터 병렬 복제 및

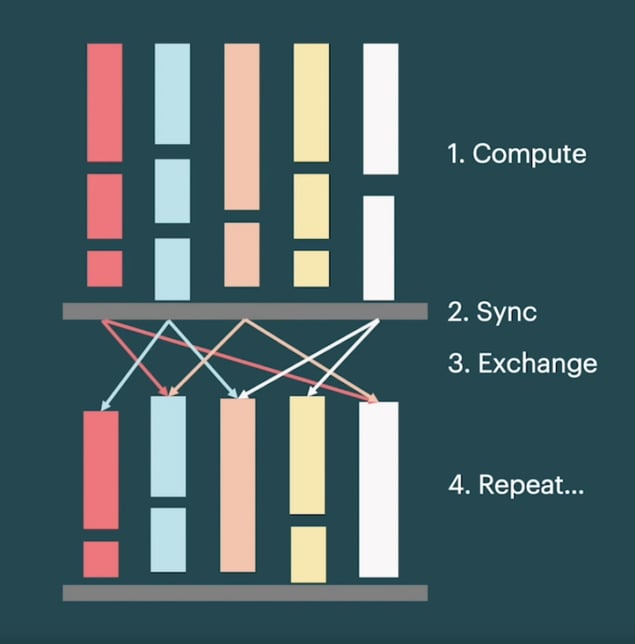

파이프라인 모델 병렬 처리를 포함하여 IPU 세트에 모델을 분산하는 다양한 방법이 있습니다. EfficientNet-B4의 크기와 IPU-POD의 규모를 고려할 때 데이터와 모델 병렬 처리의 특정 조합은 최상의 결과를 제공합니다. Poplar 소프트웨어 스택을 사용하면 프레임워크 수준에서 다양한 분산 설정을 간편하게 수행할 수 있으므로, 다양한 유형의 병렬 처리를 구성하는 최적의 방법을 빠르게 찾을 수 있습니다.

GitHub 예제에서 EfficientNet-B4의 기본 구성은 4개의 IPU에서 모델을 파이프라이닝합니다. 파이프라인 단계가 많으면 파이프라인을 채우고 비우는 데 많은 시간이 소요되어 전체 IPU 사용률이 감소합니다. 또한 IPU에서 워크로드의 균형을 유지하기 위해 더 많은 주의가 필요합니다. 파이프라인 단계의 수를 2개로 줄일 수 있다면 이러한 문제를 극복하고, 복제본 수를 두 배로 늘릴 수 있습니다.

두 개의 IPU에 EfficientNet-B4를 맞추기 위해 다음 세 가지 기법이 사용됩니다.

- 16비트 부동소수점 및 마스터 가중치 사용

- 로컬 배치 크기 축소

- 그래프코어 연구의 'EfficientNet을 더 효율적으로 만들기' 블로그 및 논문에서 설명된 대로 G16 버전의 EfficientNet 사용

IPU는 기본적으로 16비트 및 32비트 부동소수점 숫자 표현을 지원하므로 사용자가 애플리케이션에 있는 다양한 텐서의 표현을 유연하게 조정할 수 있습니다. FP32 마스터 가중치를 저장해야 하는 경우 모델 매개변수의 복사본이 훈련 전반에 걸쳐 완전한 정확도로 저장됩니다. EfficientNet의 경우 FP16 마스터 가중치를 사용하고 가중치 업데이트에 확률적 반올림(Stochastic Rounding)을 사용할 때 성능이 여전히 유지될 수 있다는 것이 확인되었습니다.

활성화를 저장하는 데 필요한 메모리는 배치 크기에 따라 조정되므로 훈련에 영향을 주지 않고 활성화 오버헤드를 줄이는 방법을 고려하는 것이 중요합니다. 활성화 재연산은 역방향 패스에 필요할 때 활성화를 재연산할 수 있는 방법입니다. 이를 통해 연산과 메모리 간의 절충점을 쉽게 찾을 수 있습니다. 이 방법은 Poplar에서 이용할 수 있으며, 파이프라이닝 API를 통해 프레임워크 수준에서 쉽게 액세스할 수 있습니다. EfficientNet-B4를 사용하면 활성화 재연산을 통해 로컬 배치 크기 3을 맞출 수 있습니다. 이러한 구성을 사용하면 미니 배치를 분산할 복제본이 두 배가 되므로 4단계 파이프라인 설정보다 더 많은 샘플을 병렬로 처리할 수 있습니다. 이 작업에는 배치 독립적인 정규화 방법인 그룹 정규화(Group Norm)가 사용됩니다. 이 모델에는 배치 간 종속성이 없기 때문에 메모리에 포함할 수 있는 모든 로컬 배치 크기를 사용할 수 있고 그래디언트 축적(GA) 횟수를 늘려서 간편하게 원하는 전역 배치 크기를 얻을 수 있습니다. 따라서 모델의 훈련 역학에 영향을 주지 않으면서도 활성화를 메모리에 포함할 수 있습니다.

컨볼루션 그룹의 크기를 1에서 16으로 늘리고 (그에 따라 FLOP 및 매개변수의 증가를 보상하기 위해 확장 비율을 줄이면) EfficientNet에서 MBConv 블록의 메모리 오버헤드가 감소합니다. 이러한 내용은 그래프코어 연구의 '

EfficientNet을 더 효율적으로 만들기' 논문에 자세히 소개되어 있으며, 그래프코어

블로그에도 요약되어 있습니다. 메모리 절약 외에도 이러한 모델 변형은 ImageNet 검증 정확도를 높이는 데도 도움이 됩니다.

이 세 가지 기법을 사용하면 옵티마이저 상태를 스트리밍 메모리로 오프로드하지 않고도 두 개의 IPU에 모델을 맞출 수 있으므로 높은 처리량의 훈련을 진행할 수 있습니다.

데이터 IO

IPU-POD와 같은 강력한 AI 가속기 시스템에서 머신러닝 모델을 훈련할 때 일반적인 병목 현상은 호스트에서 처리하기에 충분한 데이터를 모델에 공급합니다. PopRun은 여러 프로그램 인스턴스에서 애플리케이션을 분산하여 실행함으로써 이러한 병목 현상을 완화하도록 돕는 명령줄 유틸리티입니다. 각 인스턴스의 IO는 해당 호스트 서버에서 관리하므로, 모델에 데이터를 제공할 수 있는 속도에 제한을 받지 않고 다양한 IPU-POD 시스템으로 모델을 확장할 수 있습니다.

ImageNet 데이터 세트는 원래 INT-8로 표시되지만, 일반적으로는 전처리의 일환으로 호스트에서 더 높은 정밀도의 부동소수점 데이터 유형으로 캐스트됩니다. 데이터가 IPU에 있을 때 이러한 전환을 적용하면 입력 데이터가 더 낮은 정밀도로 IPU로 스트리밍될 수 있으므로 통신 오버헤드가 감소합니다. 또한 데이터가 모델에 공급되는 속도를 높여 처리량을 더욱 늘릴 수 있습니다.

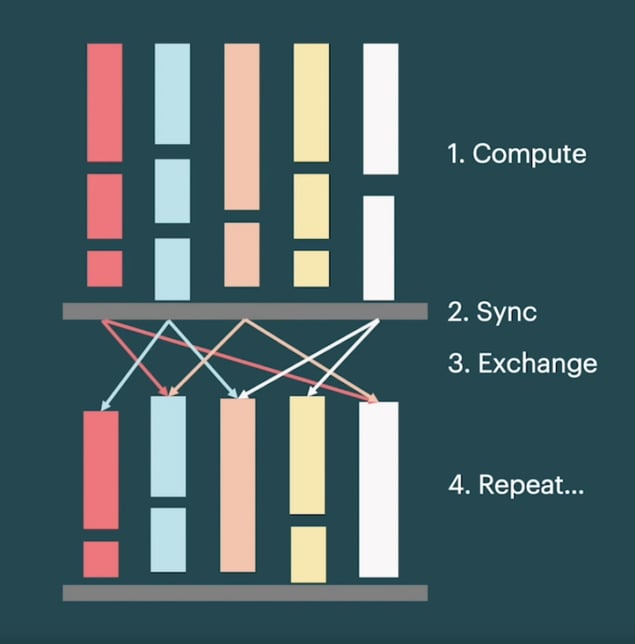

이러한 실행 체계를 통해 Poplar는 수십만 개의 타일에서 운영을 효율적으로 병렬화할 수 있습니다. IO가 제한된 애플리케이션의 경우 모든 타일에서 기본 BSP 패러다임이 성능을 제한합니다. Poplar는 비동기화 방식으로 일부 타일을 스트리밍 데이터에 할당하고 나머지 연산 타일은 BSP 패러다임에 따라 실행함으로써 이러한 문제를 해결합니다. 중복 IO는 IO 병목 현상을 완화하는 동시에 확장성이 높은 실행 체계를 가능하게 합니다. 위 방식들을 사용하는 것과 더불어, IPU당 1,472개 타일 중 32개를 IO 중첩에 할당하고 최대 3개의 데이터 배치를 미리 가져온 결과, 모든 시스템 규모에서 놀라운 처리량을 달성할 수 있었습니다.

배치 크기 확장

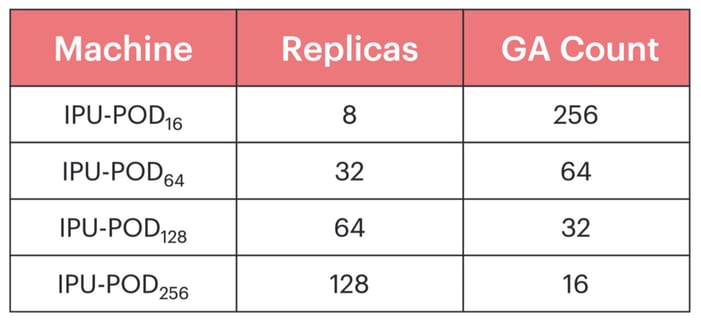

IPU-POD128 및 IPU-POD256과 같은 대규모 시스템에서 훈련하려면 대규모 전역 배치 크기를 사용하는 것이 좋습니다. 이렇게 하면 많은 복제본에서 데이터 샘플 처리를 병렬화할 수 있고, 각 복제본이 효율성을 유지하기에 충분한 작업을 수행할 수 있습니다. 또한 복제본 간의 그래디언트를 줄이는 비용을 분할 상환하기 위해 그래디언트 축적(GA)이라는 방식을 사용하여 복제본 간에 통신하고 가중치를 업데이트하기 전에 여러 정방향 및 역방향 패스에서 그래디언트를 로컬로 축적합니다. 따라서 전역 배치 크기는 로컬 배치 크기, 복제본 수, 그래디언트 축적 수의 곱입니다.

'EfficientNet을 더 효율적으로 만들기' 논문에서 가져온 그래프코어의 기준은 전역 배치 크기 768을 사용합니다. 로컬 배치 크기가 3인 경우 IPU-POD256에서 반복 훈련당 두 개의 로컬 배치만 생성되므로, 파이프라인 설정을 충분히 활용하지 못하고 빈번한 고비용 가중치 업데이트와 씨름해야 합니다. 하지만 단순히 전역 배치 크기를 늘리면 일반화 성능이 저하됩니다. 이 현상은 많은 머신러닝 애플리케이션,

특히 컴퓨터 비전에서 일반적으로 발생합니다. 따라서 그래프코어는 모든 IPU-POD 시스템에서 높은 처리량을 유지할 만큼 충분히 크지만 뛰어난 통계적 효율성을 확보할 만큼 작은 전역 배치 크기를 추구합니다.

배치 크기, 학습률, 예열 에포크 수, 운동량 계수, 가중치 감쇠에 대해 초매개변수 스윕(Hyperparameter Sweep)을 수행한 결과, 기존 EfficientNet-B4 구현과 비교하여 성능 손실 없이 전역 배치 크기 6144를 달성할 수 있었습니다. 이 배치 크기에서는 고려되는 모든 IPU-POD에서 높은 그래디언트 축적 횟수를 유지할 수 있습니다.

성능 결과

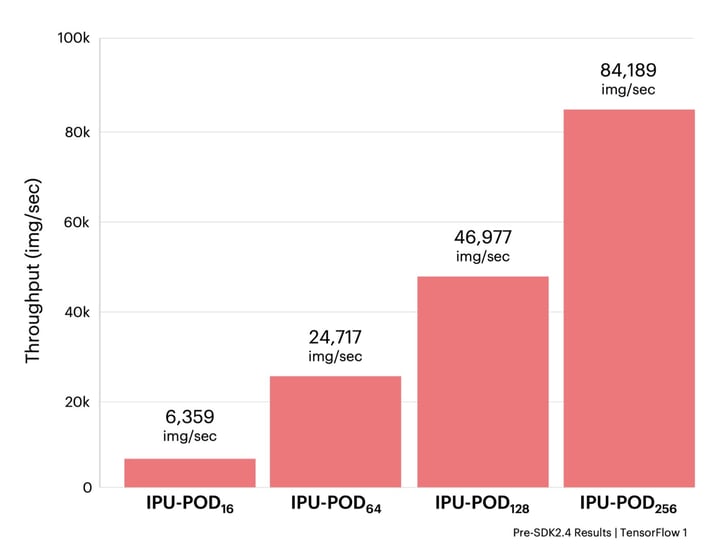

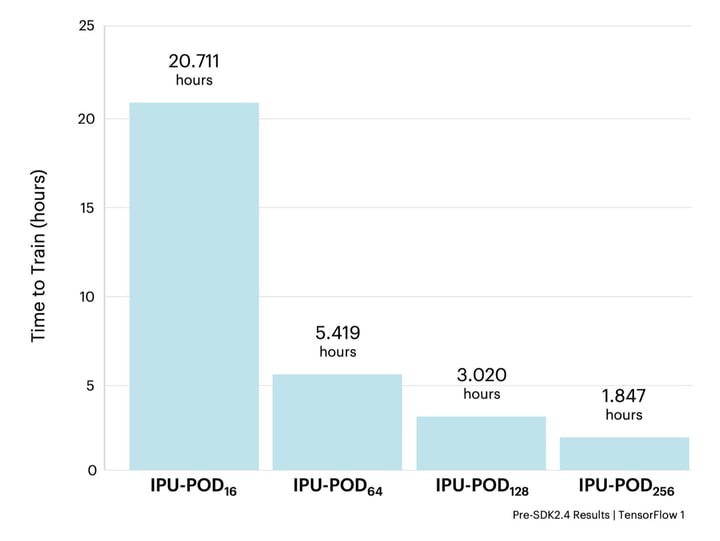

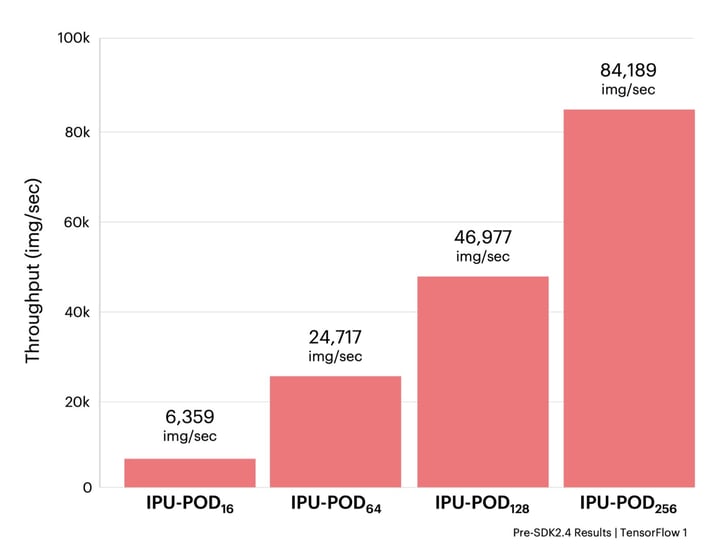

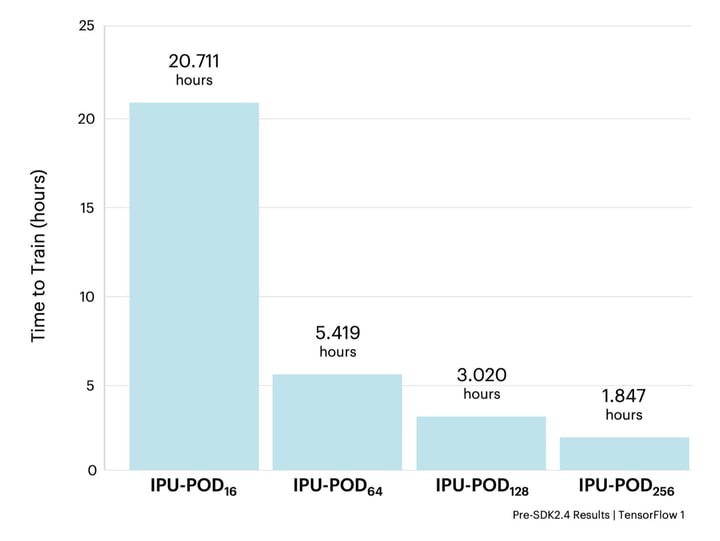

이제 유연한 초매개변수 구성을 통해 다양한 IPU-POD 시스템에서 EfficientNet-B4에 대해 높은 처리량의 훈련을 진행할 수 있습니다. 기존 EfficientNet 논문에 따르면 350회 에포크 동안 훈련합니다. 'EfficientNet을 더 효율적으로 만들기' 논문은 EfficientNet 모델 제품군이 기본 해상도에서 미세 조정하기 전에 더 낮은 이미지 해상도에서 사전 훈련될 수 있음을 보여 주었지만, 저희는 다른 구현과 비교할 수 있도록 원래 해상도를 유지했습니다.

모든 실험은 IPU-POD의 크기에 따라 복제본 수와 그래디언트 축적 수를 조정함으로써 동일한 기본 머신러닝 초매개변수 구성을 사용했습니다. 그 결과, 82.54 ± 0.13%의 검증 정확도로 모두 수렴했습니다.

위 결과는 주요 GPU 하드웨어의 결과와 대조적으로 IPU 기반 시스템에서 EfficientNet이 얼마나 빠르게 훈련될 수 있는지 보여 줍니다. 신속한 모델 훈련은 혁신가가 새로운 아이디어를 빠르게 반복하고 테스트하는 데 필수적입니다. 그래프코어는 EfficientNet-B4를 2시간 이내에 훈련하여 혁신까지 걸리는 기간을 며칠에서 몇 시간으로 단축할 수 있습니다.

이러한 속도 향상은 많은 컴퓨터 비전 애플리케이션이 레거시 프로세서 아키텍처의 제한을 받지 않을 경우 대규모로 훨씬 더 빠르게 훈련될 수 있음을 보여 줍니다. EfficientNet과 같은 차세대 컴퓨터 비전 모델은 그래프코어의 IPU-POD 시스템과 같은 새로운 하드웨어와 함께 사용될 때 CT 스캔 분석 및 동영상 업스케일링에서 결함 진단 및 보험 청구 확인에 이르기까지 다양한 비전 관련 사용 사례를 가속화하는 데 도움이 됩니다.

이러한 구성은 그래프코어의 GitHub 예제에서

지금 시도해 볼 수 있습니다. (참고: 모든 IPU-POD 시스템의 최신 구성은 Poplar SDK 2.4 릴리스로 업데이트됩니다.)

이 기사의 원본은 Towards Data Science에 게시되었습니다.

감사합니다.

이 연구에 공헌한 Dominic Masters와 Carlo Luschi에게 감사를 드립니다. 또한 아낌없는 지원과 인사이트를 제공한 그래프코어의 다른 동료들에게도 감사를 표합니다.

모든 실험은 IPU-POD의 크기에 따라 복제본 수와 그래디언트 축적 수를 조정함으로써 동일한 기본 머신러닝 초매개변수 구성을 사용했습니다. 그 결과, 82.54 ± 0.13%의 검증 정확도로 모두 수렴했습니다.

모든 실험은 IPU-POD의 크기에 따라 복제본 수와 그래디언트 축적 수를 조정함으로써 동일한 기본 머신러닝 초매개변수 구성을 사용했습니다. 그 결과, 82.54 ± 0.13%의 검증 정확도로 모두 수렴했습니다.